# XC6200 Field Programmable Gate Arrays

June 1, 1996 (Version 1.0)

Advance Product Specification

#### **Features**

- · Advanced Processor-Compatible Architecture

- FastMAP<sup>™</sup> interface allows direct processor read/ write access to all internal registers in user design with no logic overhead

- All user registers and SRAM control store memory mapped onto processor address space

- Programmable data bus width (8, 16, 32-bits)

- Easily interfaced to most microcontrollers and microprocessors

- High-Performance Sea-of-Gates FPGA

- Up to 16K configurable cells

- Abundant registers, gates and routing resources

- Extremely high gate count for structured logic or datapath designs

- · High Capacity Distributed RAM

- High speed SRAM control store

- 2 bytes of synchronous RAM per cell

- High Speed Flexible Interconnect Architecture

- Low delay hierarchical routing scheme gives large number of fast 'longlines' (Fastlanes)

- Any cell can be connected to any other

- Suited to both structured synchronous cell data path type designs or irregular random logic

- Completely flexible clocks and clears for registers

- 4 Global low-skew signals

- >110MHz flip-flop toggle rates

- · Extremely Flexible Cell Architecture

- Over 50 distinct logic functions per cell

- One register and gate/multiplexer possible for every cell

- Advanced Dynamic Reconfiguration Capability

- High speed reconfiguration via parallel CPU interface

- Unlimited reprogrammability

- Full or partial reconfiguration/context switching possible

- Ideal for custom computing applications

- · Flexible Pin Configuration

- All User I/O's programmable as in, out, bidirect, tristate or open drain.

- Configurable pull-up/down resistors

- CMOS or TTL logic levels

- 8, 16, 32-bit CPU interface

- Testability

- Pre-tested volume part

- JTAG capability with library macrocells

- XACTstep Series 6000 Development System

- Implement designs using familiar tools like Viewlogic and Synopsys

- Use PC or Unix workstation platforms

- Fully automatic mapping, placement and routing

- Interactive Physical Editor for design optimization

- Large Xilinx parts library for schematic capture

- VHDL synthesis

Table 1: The XC6200 Family of Field-Programmable Gate Arrays

| Device              | XC6209 1       | XC6216          | XC6236 <sup>1</sup> | XC6264           |

|---------------------|----------------|-----------------|---------------------|------------------|

| Max Logic Gates     | 13,000         | 24,000          | 55,000              | 100,000          |

| Typical Gate Range  | 9,000 - 13,000 | 16,000 - 24,000 | 36,000 - 55,000     | 64,000 - 100,000 |

| Number of Cells     | 2304           | 4096            | 9216                | 16384            |

| Max. No. Registers  | 2304           | 4096            | 9216                | 16384            |

| Number IOB's        | 192            | 256             | 384                 | 512              |

| Cell Rows x Columns | 48x48          | 64x64           | 96x96               | 128x128          |

| Max. RAM (bits)     | 36K            | 65K             | 147K                | 262K             |

Notes: 1. Planned Product

# Description

The XC6200 family is a new type of high performance Field Programmable Gate Array (FPGA) from Xilinx.

The XC6200 series is a family of fine-grain, sea-of-gates FPGAs. These devices are designed to operate in close cooperation with a microprocessor or microcontroller to provide an implementation of functions normally placed on an ASIC. These include interfaces to external hardware and peripherals, glue logic and custom coprocessors, including bit level and systolic operations unsuited for standard processors.

XC6200 FPGAs can provide extremely high gate counts for data path or regular array type designs. In these cases the actual gate count may be considerably higher than those given in Table 1.

An XC6200 part is composed of a large array of simple, configurable cells. Each basic cell contains a computation unit capable of simultaneously implementing one of a set of logic level functions and a routing area through which intercell communication can take place. The structure is simple, symmetrical, hierarchical and regular, allowing novice users to quickly make efficient use of the resources available.

The nearest-neighbor interconnect of the cells is supplemented with wires of length 4, 16 and chip-length (CL) cells, called FastLane-4, 16 and CL respectively, which provide low-delay paths for longer connections. In addition there are four global input signals which provide a low-skew distribution path for critical high-fan-out nets such as clocks and initialization signals.

An XC6200 part is configured by the content of an integral, highly stable six-transistor SRAM control store. This allows XC6200 parts to be quickly reconfigured an unlimited number of times. The SRAM control store can be mapped into the address space of a host processor and additional support logic is provided to allow rapid reconfiguration of all or part of the device. In addition, the outputs of function units within the device can be read by a processor through the RAM interface. A host processor can read or write registers within logic implemented on the device. Data transfers can be 8, 16 or 32 bits wide, even when register bits are distributed over a column of cells. These capabilities allow XC6200 FPGAs to support virtualised hardware in which circuits running on the FPGA can be saved ('swapped out') to allow the FPGA resources to be assigned to a different task, then restored ('swapped in') at a later time with the correct internal state in their registers. Sections of the device can be reconfigured without disturbing circuits running in other sections. Thus an XC6200 FPGA in a coprocessor application can be time-shared by several processes running on the host computer.

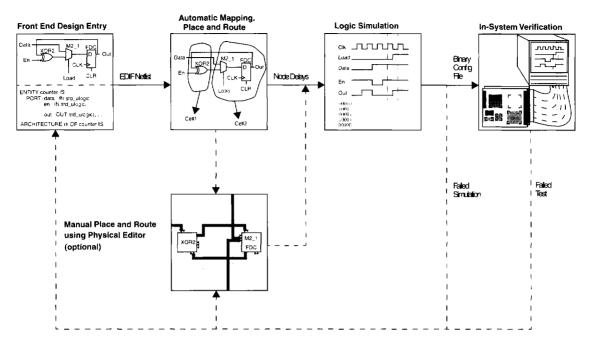

Design entry and verification are carried out with Xilinx XACT step Series 6000 software using industry-standard schematic capture, synthesis and simulation packages such as Viewlogic, Synopsys and Mentor Graphics. A comprehensive library of parts, ranging from simple gate primitives to complex macro-functions, exists to make this an easy task.

Below the top level design tools, the XC6200 product family is supported by a number of CAD tools ranging from simple symbolic editors to sophisticated cell-compilation tools. These tools will ensure that the captured design is laid out efficiently with no user intervention. Node delays can then be back-annotated to the top level logic simulator. The tools also allow for manual intervention in the layout process, if desired. Incremental design is also supported: if a design is laid out and subsequently changed, only the modified block has to be re-laid out.

The functions available within each cell provide a good target for logic synthesis programs. The simple cell architecture allows arbitrary user logic designs to be mapped onto a number of cells, rather than having to split the design up into medium-complexity mini-functions for mapping to a larger configurable logic block. Because each cell can be configured as a register, designs containing far more registers than would be possible with a larger configurable block are achievable.

# **Detailed Functional Description**

# Logical and Physical Organization

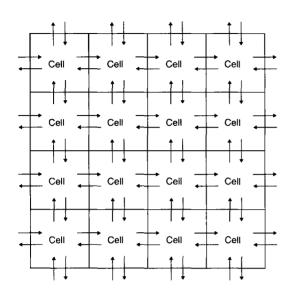

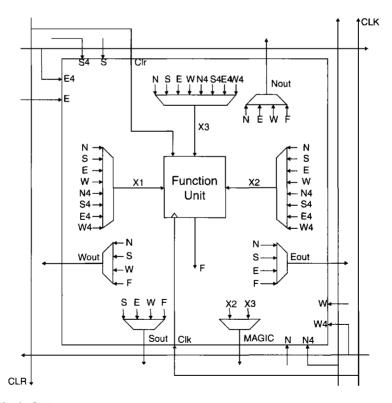

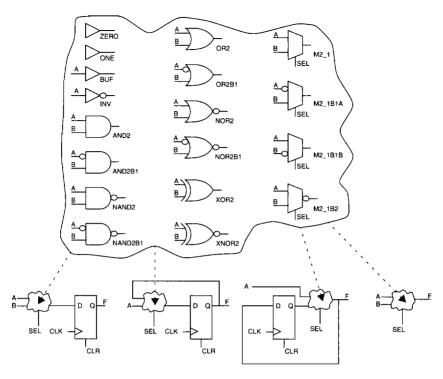

The XC6200 architecture may be viewed as a hierarchy. At the lowest level lies a large array of basic cells (Figure 1). This is the 'sea-of-gates'. Each cell is individually programmable to implement a D-type register and a 2-input logic function such as a multiplexer or gate. Any cell may also be configured to implement a purely combinatorial function, with no register. This is illustrated in Figure 7.

## Cells, Blocks and Tiles

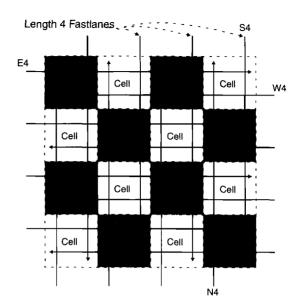

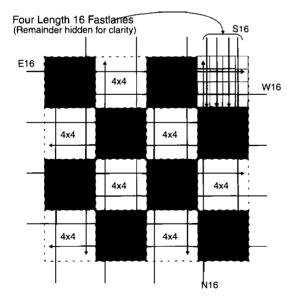

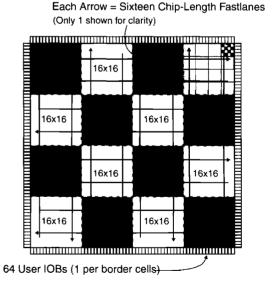

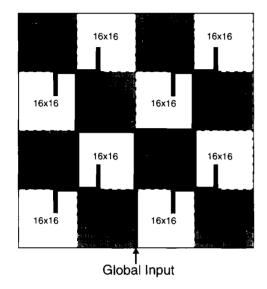

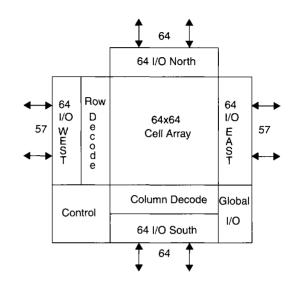

First generation fine-grain architectures implemented only nearest-neighbor interconnection and had no hierarchical routing (Figure 1). The XC6200 architecture is a second generation fine-grain architecture, employing a hierarchical cellular array structure. Neighbor-connected cells are grouped into Blocks of 4x4 cells (Figure 2) that themselves form a cellular array, communicating with neighboring 4x4 cell Blocks. A 4x4 array of these 4x4 Blocks forms a 16x16 cell Tile (Figure 3). In the XC6216 part, a 4x4 array of these 16x16 Tiles forms the central 64x64 cell array which is then surrounded by I/O pads (Figure 4).

Figure 1: Nearest-Neighbor Interconnect Array Structure

Figure 2: XC6200 4x4 Cell Block

Figure 3: XC6200 16x16 Cell Tile

Figure 4: XC6216 Device

## **Routing Resources**

Each level of hierarchy (basic cells, 4x4 cell Blocks, 16x16 cell Tiles, 64x64, etc.) has its own associated routing resources. Basic cells can route to their nearest neighbors or through the neighbor cell to its neighbor. Note that cells used for interconnect in this manner can still be used to provide a logic function. Wires of length four are provided to allow 4x4 cell blocks to route across themselves without using basic cell resources. Similarly 16x16 cell tiles provide additional wires of length 16 cells and the 64x64 array provides wires of length 64. Larger XC6200 products extend this process to 256x256 cell blocks and so on, scaling by a factor of 4 at each hierarchical level as required. Intermediate array sizes (e.g. 96x96) are created by adding more 16x16 tiles. Switches at the edge of the blocks and tiles provide for connections between the various levels of interconnect at the same position in the array (e.g. connecting length 4 wires to neighbor wires).

The longer wires provided at each hierarchical level are termed 'Fastlanes' because it is convenient to visualize the structure in three dimensions with routing at each hierarchical level being conceptually above that in lower hierarchical levels, with the cellular array as the base layer. The length-

4 Fastlanes are driven by special routing multiplexers within the cells at 4x4 block boundaries. All routing wires are directional. They are always labelled according to the signal travel direction. For example, S4 is a length-4 Fastlane heading from North to South. In Figures 2, 3 and 4 each individual cell has a length 4, 16 and CL Fastlane above it. However only a small number are shown for clarity.

The benefit of the additional wiring resources provided at each level of the hierarchy is that wiring delays in the XC6200 architecture scale logarithmically with distance in cell units rather than linearly as is the case with the first generation neighbor interconnect architectures. Since 4x4 cell block boundaries lie on unit cell boundaries, the switching function provided at 4x4 cell boundaries is a superset of that provided at unit cell boundaries. i.e it provides for neighbor interconnect between the adjacent cells as well as additional switching options using the length 4 wires. Similarly, the switching unit on 16x16 cell tile boundaries provides a superset of the permutations available from that on the 4x4 cell block boundaries. Further switching units are also provided on the 64x64 cell boundaries to provide the length CL Fastlanes.

Figure 5: XC6200 Basic Cell

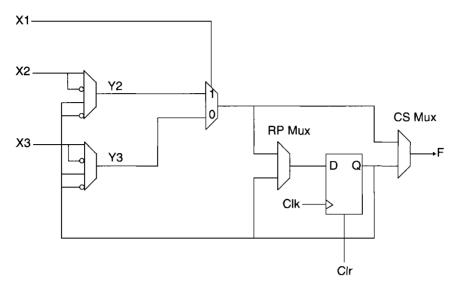

Figure 6: XC6200 Function Unit

## Magic Wires

The majority of interconnections are routed using the nearest-neighbor and Fastlane wires described above. Each cell has a further output (labelled 'Magic') which provides an additional routing resource. A cell's Magic output is not always available for routing. Its availability is dependent on the logic function implemented inside the cell. More information on the physical nature of the Magic wires is given in the section "Function Unit" on page 257.

Each cell's Magic output is routed to two distinct 4x4 block boundary switches. The Magic wire can be driven by N, S, E or W from adjacent cells or from the N4, S4, E4 or W4 Fastlanes passing over the cell. This makes it particularly useful for corner-turning (all other routing resources are straight).

The Magic wires are illustrated in Figure 8.

#### Global Wires

The XC6200 architecture permits registers within a user design to be clocked by different clocks and cleared by different asynchronous clears. Clocks and Clears may be provided by any user I/O pin or generated from user logic internally. In line with good synchronous digital design practices, it is recommended that a single global Clock and Clear are used. This minimizes the likelihood of timing problems and gives more reliable simulations.

Four Global wires (G1, G2, GClk and GClr) are provided for low skew, low delay signals. These wires are intended for global Clock and Clear or other high fan-out signals and are distributed throughout the array in a low skew pattern. A global signal can reach the function block inputs of any cell

on the array passing through very few routing switches. The four Globals are very similar. It would be possible to use GClk as a global Clear signal, however for minimum delay, it is recommended that GClk be used for global clocks and GClr for global clears. GClk and GClr can reach the inputs of any register in the array, passing through only a single routing switch. G1 and G2 may be used for secondary global clocks or clears. G1 and G2 have a slightly larger delay than GClk and GClr.

#### **Function Unit**

Figure 5 shows the basic XC6200 cell in detail. The inputs from neighboring cells are labelled N, S, E, W and those from length 4 wires N4, S4, E4, W4 according to their signal direction. Additional inputs include Clock and Asynchronous Clear for the Function Unit D-type register. The output from the cell function unit, which implements the gates and registers required by the user's design, is labelled F. The Magic output is used for routing as described earlier. The multiplexers within the cell are controlled by bits within the configuration memory. As can be seen from Figure 5, the basic cells in the array have inputs from the length 4 wires associated with 4x4 cell blocks as well as their nearest neighbor cells. The function unit design allows the cells to efficiently support D-type registers with Asynchronous Clear and 2:1 multiplexers, as well as all Boolean functions of two variables (A and B) chosen from the inputs to the cell (N,S,E,W,N4,S4,E4,W4) (Table 2). Figure 7 shows the schematic representations of the basic cell functions possible. The Magic routing output can only be used if the signal to be routed can be placed on X2 or X3.

Figure 7: Cell Logic Functions

Figure 6 shows the implementation of the XC6200 function unit. The design uses the fact that any function of two Boolean variables can be computed by a 2:1 multiplexer if suitable values chosen from the input variables and their complements are placed on its inputs. The Y2 and Y3 multiplexers provide for this conditional inversion of the inputs. The CS multiplexer selects a combinatorial or sequential output. The RP multiplexer allows the contents of the register to be 'protected'. If register protection is enabled then only the programming interface can write to the register. It will not change when the X inputs to the function unit change, even if it is clocked or cleared. This feature is useful in designs containing control registers which are only to be written by an external microprocessor. The control inputs of all the multiplexers, except the one switched by X1, come from configuration memory bits.

#### Cell Logic Functions

Each cell can be configured as any two-input gate function, any flavor of 2:1 multiplexer, constant 0 or 1, single input functions (buffer or inverter) or any of these in addition to a D-type register. This is illustrated in Figure 7. The gate names given correspond to standard Xilinx library part names for these primitives. Although three inputs are shown entering the combinatorial 'cloud', dual and single input functions are also possible (e.g. inverter + register or

register alone.) The buffer symbol is available in the CAD libraries, however the place and route software will generally optimize this out as there is no requirement for the designer to buffer signals with this architecture. This is because signals are regularly buffered by routing multiplexers. Symmetrical functions are also possible but not shown in Figure 7; e.g.  $\overline{A}$ -B (AND2B1) is shown but A- $\overline{B}$  (AND2B2) is not. This is because A and B are assigned to user signals by the logic mapping software to provide the required function. Thus, a multiplexer with inversion on the SEL input is unnecessary because the mapping software can simply swap the signal assignments for A and B.

The sources of the X1, X2 and X3 input multiplexers are set automatically by CAD software during the logic mapping phase. Table 2 shows the assignments for all the cell multiplexers to compute the various logic gate functions. A NAND2B1 is equivalent to an OR2B1 with the inputs swapped and a NOR2B1 is equivalent to an AND2B1 with the inputs swapped; therefore, these gates are not listed in Table 2.

If the register within a cell is not used in the design then a special 'fast' version of most gates can be configured, using the register to provide a constant 1 or 0. For example a fast AND gate (A•B) can be configured by setting the register to 0 during configuration and assigning Q to Y3. A is routed to X1 and B to X2. X2 is assigned to Y2. When A changes to

Table 2: Function Derivation

| Function   | X1  | X2 | ХЗ | Y2        | Y3             | RP | CS | Q   |

|------------|-----|----|----|-----------|----------------|----|----|-----|

| 0 (Fast)   | X   | X  | X  | Х         | X              | Q  | S  | 0   |

| 0          | Α   | Α  | Α  | X2        | Х3             | Х  | С  | Х   |

| 1 (Fast)   | Х   | Х  | X  | Х         | Х              | Q  | S  | . 1 |

| 1          | Α   | Α  | Α  | X2        | X3             | Х  | С  | Х   |

| BUF (Fast) | A   | Χ  | Х  | Q         | Q              | Q  | С  | 1   |

| BUF        | X   | Α  | Α  | X2        | Х3             | Х  | С  | X   |

| INV (Fast) | Α   | Х  | Х  | Q         | Q              | Q  | С  | 0   |

| INV        | X   | Α  | Α  | X2        | X3             | X  | С  | Х   |

| A•B (Fast) | Α   | В  | X  | X2        | Q              | Q  | С  | 0   |

| A•B        | Α   | В  | Α  | X2        | Х3             | X  | С  | X   |

| •B (Fast)  | Α   | X  | В  | Q         | Х3             | Q  | С  | 0   |

| •B         | A   | Α  | В  | X2        | Х3             | X  | C  | Х   |

| •B (Fast)  | Α   | В  | Х  | <u>X2</u> | Q              | Q  | С  | 1   |

| A•B        | Α   | В  | A  | X2        | <u>X3</u>      | X  | С  | Х   |

| A+B (Fast) | Α   | X  | В  | Q         | ХЗ             | Q  | С  | 1   |

| A+B        | Α   | Α  | В  | X2        | Х3             | X  | С  | Х   |

| Ā+B (Fast) | Α   | В  | X  | X2        | Q              | Q  | С  | 1   |

| Ā+B        | Α   | В  | Α  | X2        | <u>X3</u>      | ×  | С  | X   |

| A+B (Fast) | A   | Χ  | В  | Q         | X3             | Q  | С  | 0   |

| A+B        | Α   | A  | В  | X2        | X3             | Х  | С  | X   |

| A⊕B        | Α   | В  | В  | X2        | Х3             | X  | С  | Х   |

| Ā⊕B        | Α   | В  | В  | X2        | X3             | Х  | С  | Х   |

| M2_1       | SEL | Α  | В  | X2        | Х3             | Х  | С  | Х   |

| M2_1B1A    | SEL | Α  | В  | X2        | ХЗ             | Х  | С  | Х   |

| M2_1B1B    | SEL | Α  | В  | X2        | <del>X</del> 3 | X  | С  | Х   |

| M2_1B2     | SEL | Α  | В  | X2        | <del>X3</del>  | Х  | С  | Χ   |

0, Y3 is selected and F is forced low as soon as the X1-controlled multiplexer switches. In the normal AND gate, there would be an additional delay as A propagated through the Y3 multiplexer. Fast or normal gates may be specified by the designer but, for optimal layout density, this is best left to the logic mapping software.

The multiplexer functions have a straightforward mapping with fixed assignments to X1,X2 and X3, and Y2 and Y3 providing input inversions as required.

## Routing Switches

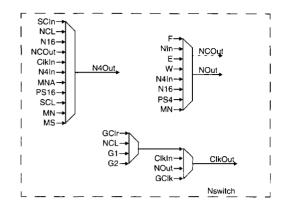

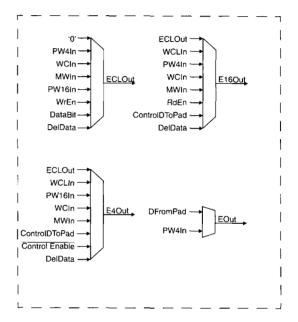

As described earlier, each cell within a 4x4 block is able to drive its output to its nearest neighbors to the N,S,E and W. In addition to this, cells at 4x4 block boundaries are also able to drive their outputs onto length-4 Fastlanes. Special switch units are provided around each 4x4 block boundary to facilitate these connections. This is illustrated in Figure 8. These switches also allow higher levels of hierarchical routing (e.g. length – 16 and CL Fastlanes) to be connected to length-4 Fastlanes.

Figure 8 also shows the connections for each cell's Magic output. Each Magic output is routed to two destinations for increased routing flexibility. The two connections are labelled M and MA. The Magic wires allow cell outputs to jump to the edge of the 4x4 block and hence onto Fastlanes or into the next 4x4 block. They are also a particularly efficient way of making large busses turn corners.

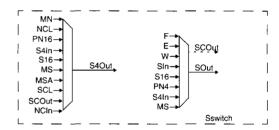

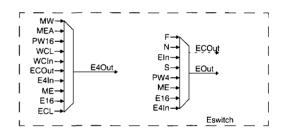

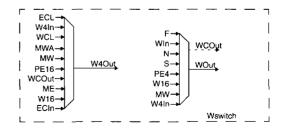

N,S,E and W switches are similar, however the N switches contain additional multiplexers to drive the register Clock lines. The contents of the boundary switches are shown in Figure 9 through Figure 12. The multiplexers driving the NOut, SOut, EOut and WOut lines are actually implemented within the cell adjacent to the switch. These multiplexers take the place of the neighbor multiplexers found in the basic cell (see Figure 5). Boundary cells contain additional RAM bits to control the larger multiplexers. An additional output is available from these multiplexers. This output reflects the output that would have come from the cell's neighbor multiplexer had it been a basic non-boundary cell. To distinguish this from the output of the boundary switch (NOut, SOut, EOut or WOut), it is suffixed with a 'C' (Cell); e.g. NC for an Nswitch. NC will be one of NIn, E, W,

or F depending on the least-significant two bits of the NOut multiplexer select lines. Hence NC will be identical to NOut if NOut is one of F, NIn, E or W. If NOut is one of N4In, N16, PS4 or MN then NC will be one of F, NIn, E or W depending on which signal is routed to NOut. The 'C' signal will be one of the upper four inputs to the 8:1 multiplexers shown in Figure 9 through Figure 12, the actual value being selected by the two least-significant multiplexer select lines. Similar 'C' signals are generated in the Sswitch, Eswitch, and WSwitch.

The S4 input to the NOut multiplexer in the Nswitch is actually the S4 *input* to the adjacent Sswitch in the 4x4 block immediately to the North of this block. This should not be confused with the S4Out signal from that block's Sswitch. This is also true of some of the other inputs to the multiplexers in other boundary switches. To avoid confusion, these inputs are prefixed with the letter 'P' (for Previous). e.g. PS4. This feature allows Fastlane wires to perform U-turns.

Figure 8: Routing Switches at 4x4 Block Boundary

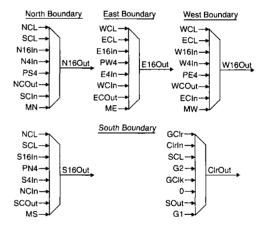

Figure 9: Contents of Nswitch

Figure 10: Contents of Sswitch

Figure 11: Contents of Eswitch

Figure 12: Contents of Wswitch

4- 260

## **Clock Distribution**

As described previously, register clock inputs may be driven from any source but it is recommended that the GClk signal is used. GClk also has the advantage that it can be stopped by writing to the Device Configuration Register. The Global wires enter the part through dedicated input pins and are distributed in a special low-skew 'H' pattern (Figure 13). Each vertically aligned (South to North) group

Figure 13: Low Skew 'H' Distribution Of Global Signals (XC6216)

of four cells within a 4x4 block is clocked by its own clock source. This is driven from a multiplexer in the Nswitch immediately to the South of the group of cells. The connections for this multiplexer are shown in Figure 9. ClkOut drives the Clk inputs to each of the four cells in the group. As can be seen from Figure 9, the register clock for each group of four cells can be driven by ClkIn, NOut, GClk. GCIr, G1, G2 or NCL. ClkIn is the ClkOut from the 4x4 block to the South, allowing vertical daisy-chaining of clock signals. NOut is the N output from the cell associated with the Nswitch. This can be used to provide local user-generated or gated clock signals if required. GClk is the Global Clock signal direct from the device GClk input. Clearly this signal only has to pass through one 4:1 multiplexer whereas GCIr, G1 and G2 have to pass through two. This is one reason why there is less delay on GClk.

It is also possible to route North chip-length Fastlanes onto the Clock lines. This allows up to 64 (for a XC6216 device) locally used clocks to be provided that can still run the entire length of the chip with minimal skew. These local clock signals may be generated internally (e.g. by dividing a faster clock) or sourced directly from the device programmable I/O pins.

Where a fast clock is required by only a small fraction of the logic on the device it may be preferable to employ user interconnect resources rather than a Global or Chip-Length Fastlane, since limiting fast clock distribution to the area of the device where it is required will reduce power consumption.

#### Clear Distribution

Register Clear inputs are routed in a similar manner to Clock inputs. In this case vertical groups of 16 cells, within a 16x16 tile, share a common Clear. Clear lines run in a Southerly direction and are sourced from the Sswitch unit of 4x4 blocks which also lie on a 16x16 boundary. All of the boundary switches at 16x16 boundaries contain additional switching multiplexers. These are illustrated in Figure 14.

ClrOut drives the Clr inputs to each of the sixteen cells in the group. The S and SCL connections allow the output of a cell to provide a user-generated local Clear signal.

Figure 14: Additional Switches at 16x16 Boundaries

# Input/Output Blocks (IOBs)

User-configurable Input/Output Blocks (IOBs) provide the interface between external package pins and the internal logic.

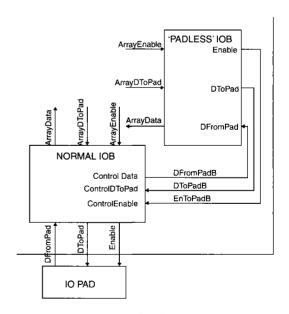

One IOB is provided for every cell position around the array border. IOBs are connected to fixed pad locations. There are more IOBs than available pads, hence some IOBs are 'padless'. However it is still possible to route signals from padless IOBs to device pins.

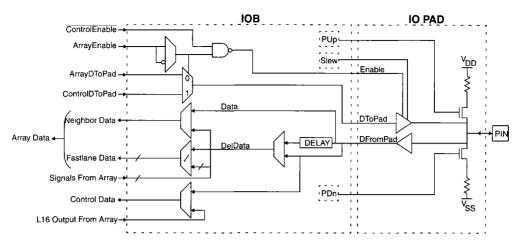

Figure 15 is a simplified diagram of an IOB and its associated IO pad. The IOB is located at the array border and the pad is located close to its device pin. The pad may be located some distance from its associated IOB. The map-

Figure 15: Input/Output Architecture

ping of IOBs to device pins is given in the pinout tables starting on page 282.

The XC6200 IOB architecture incorporates a novel and very powerful feature: every IOB has the capability of routing either an array signal or a control logic signal to/from the device pin. Every signal, including all the control signals (e.g.  $\overline{CS}$ ,  $\overline{RdWr}$ , Address Bus, Data Bus, etc.), passes through an IOB. This means that all the control signals can be routed into the logic array for use in user designs. Similarly, user logic can control the XC6200 internal control circuitry. For example a user signal could be used to drive the internal  $\overline{CS}$  signal rather than the  $\overline{CS}$  pin.

As an example of the power of this feature, an XC6200 design could include an address decoder which decoded microprocessor read/write cycles and produced appropriately retimed signals for all the parts on a board *including itself*, thereby removing the need for address decoding PAL's or discrete logic.

Each IOB has an array data input and a control data input, labelled ArrayDToPad and ControlDToPad in Figure 15. Associated with these inputs are two enable signals - Array-Enable and ControlEnable. These signals control whether the pad associated with this IOB is in the input or output mode. Each IOB also supplies ArrayData and ControlData when acting as an input.

The 'Control' signals are routed to the internal XC6200 control circuitry. If control signals are not required all the time then these IOBs can be used to route other user signals into the array. For example if only eight data bus bits were continuously required, the remaining twenty-four IOBs associated with the data bus could be used to route user signals to/from the array. ControlEnable comes either from the internal XC6200 control circuitry if there is a bidirectional control signal or output signal on that IOB, or it is tied inactive.

There are less real control signals than IOBs, hence the three control signals on some IOBs are not connected to the device control logic. These spare control signals are used to route data to and from the padless IOBs mentioned above. The control signals on the padless IOB are not used. This is illustrated in Figure 16.

Figure 16: 'Padless' IOB Configuration

The 'Control' signals are also referred to as 'B' signals later in this data sheet. ControlDToPad = DToPadB, ControlEnable = EnToPadB and Control Data = DFromPadB. Also the L16 output from the array, which can be routed onto Control Data, is referred to as DForPadB.

Three configuration RAM bits within each IOB control the programmable aspects of its IO pad. These RAM bits have no effect for padless IOBs. 'PUp' and 'PDn' enable the pull-up and pull-down resistors. The resistors may be used to tie floating logic inputs to a known value. 'Slew' slows the out-put transition time to reduce supply noise and ground-bounce. The default condition is pull-up off, pull-down off and slew on.

The Array Enable, Array Data and Control Data multiplexers are also controlled by configuration RAM bits. A fixed delay may be optionally applied to Array Data inputs. This allows the input data hold time specification to be removed.

The ArrayEnable and ArrayDToPad signals can be configured to constant 0 or 1 values within the logic array. The constant values are particularly useful for the enable signal when the pin is to function as an input or output rather than a bidirectional pin. Constant values on the data signal and a computed value on the enable signal produce open drain pull-up (DToPad=1) or pull-down (DToPad=0) pins.

During reset, all the output drivers are disabled and the pull-up resistors are enabled. The pull-up and pull-down RAM control bits have no effect. After a reset the output drivers remain in this state. For the output drivers to be enabled, the global  $\overline{\text{OE}}$  signal must be asserted (low) and a valid configuration must be present in the device ID register. The ID register is usually the last thing to be written during configuration and acts as a check that the programming interface is operating correctly. More details of this are given in the 'Programming' section on page 268. The  $\overline{\text{OE}}$  signal provides a quick way of disabling all the output driv-

ers and may be activated at any time. Only when  $\overline{OE}$  is active and there is a valid ID pattern in the ID register, do the pull-up and pull-down RAM control bits determine the IO-pad resistor configuration.

## I/O Routing

The array signals to and from the IOBs are generally just the signals which would have passed between two cells in the array. The ArrayDToPad signal in Figure 15 is actually the neighbor output from the border cell associated with the IOB. The Array Enable signal is the length-4 Fastlane output from the same cell.

Figure 17: Array Data Sources In West IOBs

The Array Data multiplexer in Figure 15 is actually a collection of multiplexers that source the neighbor, length-4. length-16 and chip-length wires into the array. South IOBs (IOBs at the South edge of the array) also source the local clock signals into the array. North IOBs source the local clear signals. This is illustrated for a West IOB in Figure 17. These multiplexers also allow a number of other internal control signals to be routed into the array: WrEn and RdEn are signals which are active during state register accesses. 'DataBit' is the state register output value for this row during a state access. Details of the timing of these signals are given in the "Parallel Programming Interface" on page 268. Note that in order to provide a minimal delay signal path into the core array, the neighbor data output from the IOB cannot select the delayed version of DFromPad. Only the un-delayed DFromPad and the Previous Length-4 Input can be routed onto the neighbor data output. Therefore the neighbor data output is unaffected by the value of the configuration memory which controls the DelData multiplexer in Figure 15.

The length-4 and length-16 routing multiplexers at the array border also expect some inputs which are not available. For example at the West edge, MEIn, ECIn, PE4In and PE16In are non-existent. These inputs are tied to ground thereby providing an abundant source of constant zeros and ones at the array border. These can be used to provide constant values to drive the Array Enable inputs to IOBs.

# OE → Reset → I/O

FastMAP Interface

Figure 18: XC6216 Logic Symbol

GCIk GCIr

Figure 19: XC6200 Logic Design Flow

# **Designing with XC6200**

The designing of XC6200 FPGAs into systems may be partitioned into three distinct activities: board design, logic design, and software design.

## **Board Design with XC6200**

An XC6200 part may be used on a board design as a microprocessor peripheral part, as an ASIC-type device or as both. In the first instance the XC6200 part will have conventional SRAM data, address and control signals. In other cases, it may only require the user defined I/O signals of an ASIC. Packaging information for the part is shown in Table 6. The number of user I/O signals will depend on the exact package used.

Several XC6200 devices may be tiled together on a board to form a larger array. The regular array structure of XC6200 devices makes this particularly easy.

The configuration RAM bits in the IOBs allow for a number of different programmable options to make interfacing to other ICs easier.

## Logic Design with XC6200

This can be approached as an ASIC type design using the function and routing architecture defined in the previous sections. An example design flow is illustrated in Figure 19. The design may be carried out in a variety of different ways. Hardware description languages such as VHDL may be

used with the synthesized design targeted to the XC6200 architecture. Alternatively, schematic capture, using the extensive Xilinx Unified Library, with commonly used front end design tools (e.g. ViewLogic PROcapture/ViewDraw) may be used. These tools produce an EDIF netlist which is subsequently passed to the underlying XC6200 place and route software. This automatically maps the user's design to the XC6200 architecture in an efficient way and provides individual node delays which can be passed back to the high level simulation tools such as Viewlogic PROsim/ ViewSim for accurate simulation. Simulation may be carried out prior to placement to check the logical correctness of the design using nominal delays. The place and route software also has optimization capability to carry out tasks such as redundant gate removal. A binary configuration file that can be written to the XC6200 device via the programming interface is also produced automatically. The underlying CAD software is highly integrated with the high level CAD tools, providing user-friendly pull-down menus and dialog boxes to carry out all tasks.

These methods allow designers with little or no knowledge of the XC6200 architecture to quickly produce large and complex designs. Some designers may wish to carry out detailed hand placement and routing to produce ultra-optimized very high-speed/small area sections in their designs. Others may wish to generate large regular structures such as systolic arrays or perform floor-planning for extra efficiency. For these cases, a sophisticated physical editor is available that allows designers to graphically modify the

automatic placement of gates/registers into cells and modify the routing as much as required. Alternatively this software may simply be used to see how the automatic placement and routing software has optimized a design. If a modification is subsequently made, then only the modified part of the design needs to be re-laid out. This incremental design process provides a very rapid change cycle during debugging.

All the design tasks may be carried out on PC or Unix workstation platforms.

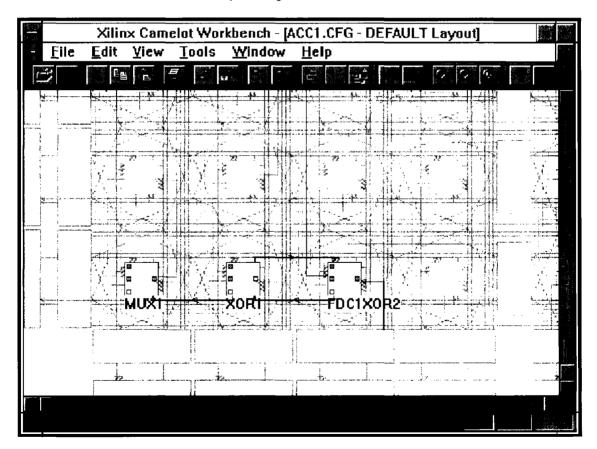

As an example, the simple accumulator circuit of Figure 20 is mapped onto the XC6200 architecture. Figure 21 shows the resulting layout as displayed by the Physical Editor running under Microsoft Windows in this case. The Physical Editor tools are also available for Unix workstations. The boundaries of basic cells within the array are denoted by the squares, with larger rectangles representing the switch units on 4 cell boundaries. The wiring resources used by the design mapped onto the array are indicated by solid black lines. When a cell function unit is used by the design

it is annotated with the instance names of the mapped primitives. The primary inputs and outputs are not shown in this example.

Figure 20: Accumulator Schematic

Figure 21: Accumulator Physical Editor View

The inputs and outputs to the function unit are connected to the edges of the cell box. The CAD plot shows all the routing resources available. To the left of each cell the six wires running in a Southerly direction are: SCL, S16, Clr, S4. Magic and S. The signal direction is indicated with arrow heads. S, S4 and Clr are shown entering the cells on the left edge of the cell boxes. The two outputs on the left edge of the cell box are Magic and SOut. The inputs and outputs on the remaining three cell box edges follow a similar pattern. The Clk input on the right hand cell box edge is denoted with a clock '<' symbol.

The Physical Editor allows cells to be selected and moved. The inter-cell routing rubber-bands and adapts automatically to the new placement. The routing may also be manually modified if desired.

## Software Design with XC6200

This is the design of a program for the host processor which interacts with a design running on the XC6200 FPGA. Here various registers within the XC6200 design appear as locations within the processor's memory map. In addition, the configuration memory of the device appears within the memory map and portions of the device can be reconfigured as required. Predefined device drivers and an efficient run-time library are available to make optimal use of the high speed reconfiguration capabilities with minimal development time.

# **Register Access**

The XC6200 architecture supports direct accesses from the processor to nodes within the user's circuit: the output of any cell's function unit can be read and the flip-flop within any cell can be written. During state reads a number of cell outputs are routed onto the CPU data bus. The signal which is actually read is the inverse of F in Figure 6 (= Q or  $\overline{D}$ ).

These accesses are carried out through the control store interface and involve no additional wiring within the user's design. The CPU interface signals involved in addressing the cell state can be routed into the configurable array so that user circuits can detect that an access has been made and take appropriate action: for example, calculate a new value for an output register or process a value placed in an input register.

In many applications this access to internal nodes will be the main path through which data is transferred to the processor and in some coprocessor type applications it may be the only external I/O method: user programmable I/O pads may not be required at all.

To allow high bandwidth transfers between the processor and internal nodes it is necessary to be able to transfer a complete processor data word of up to 32 bits in one memory cycle. For this reason, access bits are mapped into a separate region of the device address space from configuration bits so that all the bits in a word contain access bits.

Figure 22: XC6216 Block Diagram

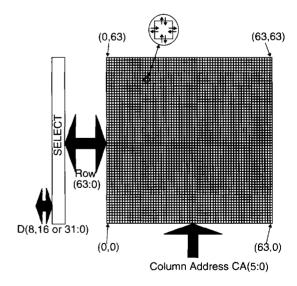

Figure 22 is a block diagram of the XC6216 part, showing the row and column address decoders. Figure 23 shows the mapping of this area of the address space: there are 64 I/O signals from each column of cells and a 6-bit column address selects a particular column of cells to access. This row and column addressing scheme puts a constraint on the placement of registers within the user's design that are to be accessed word-wide: they must be on the same column of cells within the array.

Figure 23: Memory Mapped I/O

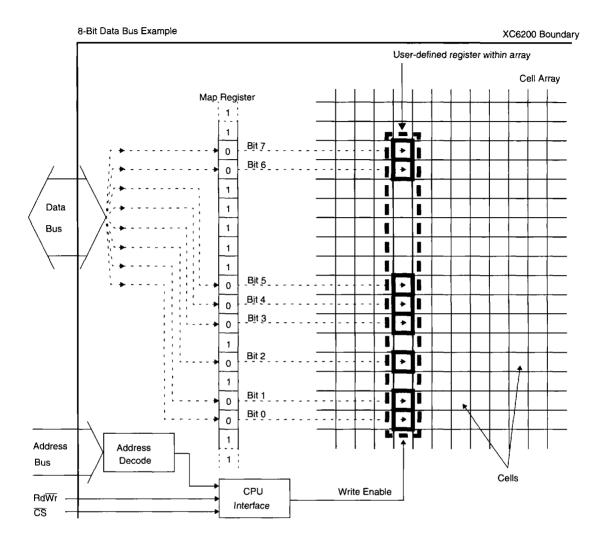

## **Map Register**

The XC6200 architecture also provides a mechanism for mapping the 64 possible cell outputs onto the 8,16 or 32-bit external data bus, selecting only those cells that implement bits of the register to be accessed. Without this unit the processor would have to implement a complex sequence of shift and mask operations to discard those bits corresponding to cells not within the register, or the user would have to constrain the layout so that the register bits were in adjacent cells. The mechanism provided takes the form of a 64bit map register, one bit for each row I/O signal from the array. This map register can be read and written through the control store interface and is set up prior to state accesses. A logic 0 in the map register indicates that the cell in the corresponding row is part of the register to be accessed. The unit maps rows from the cell array onto external data lines starting with the least significant bit: thus the first row with a 0 in the map register will connect to external data bus bit 0, the second row with a 0 in the map register to data bus bit 1 and so on.

This technique puts a further constraint on the user's layout: the cells implementing the bits of the register must be ordered so that less significant bits occur below more significant bits. However, there are no constraints about the relative separations of the cells. In practice these two placement constraints: cells occurring in the same column and in order vertically are easy to meet in datapath type designs.

Normally, the map register will be set once to indicate the placement of the user I/O register that will then be accessed many times. Therefore the two write operations required with a 32-bit bus to set up the map register represent a small overhead. In data path type designs where several registers are required, for example two input operand registers and a result register, it is easy to ensure that the corresponding bits of the registers occur on the same row but different columns of the array so that the same map register value can be used with different column addresses to access the various registers.

If more '0's exist in the map register than there are valid data bus bits then a form of wildcarding occurs during writes. The data bus bits are allocated to the rows of the array with a '0' in their map register bit. Once all of the data bus bits have been allocated, Bit 0 of the data bus is allocated to the next row whose map register bit is a '0', Bit 1 of the data bus to the next row and so on. This feature means that an entire column of state registers can be written with a single 8-bit write. For example, if the map register contains all '0's and the CPU writes FFh to a particular column. All the state registers in that column will be written with a '1'. The default state of the map register is all '0's.

During reads, if there are more '0' bits in the map register than data bus bits, the first rows with '0' bits are mapped onto the bus. If there are less '0's in the map register than data bus bits, the upper data bus bits, which are not mapped, will be read as '1's during CPU reads and ignored during CPU writes.

An example of map register operation is shown in Figure 24. The position of the user-defined register within the cell array is defined by the '0's in the 64-bit map register. Similar registers could be defined for every column in the array if desired.

There is a delay after a write to the map register before the change takes effect. No state accesses should be carried out during this time.

## Mask Register

A mask unit controlled by a 32-bit register is placed between the external data bus and the internal data connections. When the external data bus is 8 or 16 bits wide only the bottom 8 or 16 bits of this register are significant. A logic '1' in a bit of this register indicates that the corresponding bit of the internal data bus is *not* relevant. Bit locations corresponding to '1's in the Mask Register will retain their values when written. On a write operation the corresponding bit line will not be enabled and the state information for that bit will not be changed. When the device is reset the Mask Register will contain all logic 0's corresponding to all data bus bits valid.

During CPU reads, valid register bits which are disabled will be read as '0'. Invalid bits (bits which do not physically exist for the register being read) may be read as '0' or '1'.

The mask register does not affect state register accesses. In this case the map register can be used to prevent certain bits being modified.

# **Programming**

The binary data for configuring an XC6200 device, generated by CAD software from the textual description of a user design, must be downloaded into the part itself. This may be performed in several ways. Generally, the fastest and most efficient way is by writing directly to the control store, mapped into the address space of a host processor. If a microprocessor or other parallel data source is not available, then the serial programming interface may be used.

# **Parallel Programming Interface**

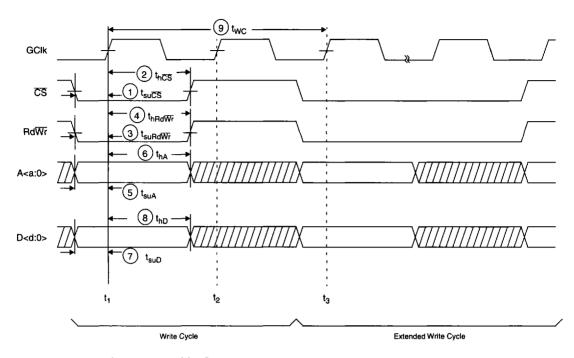

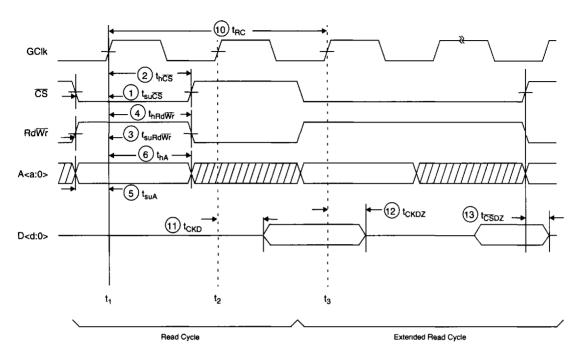

The XC6200 FPGA has a conventional programming interface for static RAM, based on Chip Select ( $\overline{CS}$ ) and Read/Write (Rd $\overline{Wr}$ ) control signals. The  $\overline{CS}$  signal can be used to address a single part within an array of devices and allows data to be read or written. Timing for these signals is illustrated in Figures 28 and 29. These figures show that the programming interface is synchronous. The GClk input is used to sample all the interface signals. GClk is also used when accessing user registers as illustrated in Figure 24. This is an important point, as only registers clocked directly by GClk can be reliably read or written using this method.

Figure 24: Internal Register Access

Figure 29 shows two separate read cycles - a normal cycle immediately followed by an extended cycle. In the normal read cycle  $\overline{CS}$  is sampled low on the first rising GClk edge  $(t_1)$  and high on the next  $(t_2)$ . The data bus is then driven until the next rising GClk edge  $(t_3)$ . In cases where this is not long enough, the read cycle can be extended by keeping  $\overline{CS}$  asserted beyond  $t_2$ . This is equivalent to adding wait states. In this case the data bus is driven until  $\overline{CS}$  is deasserted.  $\overline{CS}$  should not be allowed to go high and low again. This would cause another cycle to begin.  $\overline{CS}$  is sampled on every rising GClk edge. Other CPU interface signals such as  $\overline{RdWr}$  and the Address Bus are only sampled on the first GClk edge of the cycle  $(t_1$  for the first cycle and  $t_3$  for the second in the figure examples).

Extended write cycles are also possible, however these are functionally no different to normal write cycles, the data and address busses still being sampled on the first rising GClk edge of the cycle (t<sub>3</sub> in Figure 28).

CS must always be sampled as a '1' before the next cycle can begin. In Figure 29 the extended read cycle starts immediately after the normal read cycle at time t<sub>3</sub>. A write cycle could not start until the *next* rising GClk edge as the data from the read cycle is still on the data bus.

The SRAM programming interface is supplemented by additional hardware resources designed to minimize the number of processor cycles required for reconfiguration.

These resources are initially inactive after a reset so the device looks like an SRAM.

The control store layout is designed to minimize the overhead of computations required for dynamic access while maintaining adequate density to minimize the external storage required for device configurations. When an external processor is used to configure the device it may be convenient to use a compressed format of the configuration information.

A feature of the XC6200 architecture is that a rectangular area of cells specified as a hierarchical block within a user's design corresponds directly with a rectangular area within the configuration memory of the XC6200 device. This means that a block within the user's design can be dynamically replaced with another block by the host processor, reconfiguring only the corresponding area of the control store. The binary data for both blocks can be pre-calculated from the cellular design and the actual replacement can be carried out very rapidly using a block transfer operation.

The format of the address bus to the XC6216 device is shown in Table 3. Larger XC6200 devices have proportionally more bits allocated to row and column addresses.

Table 3: Address Bus Format (XC6216)

| Mode(1:0) | Column(5:0) | Column Offset<1:0> | Row(5:0) |

|-----------|-------------|--------------------|----------|

| 15:14     | 13:8        | 7:6                | 5:0      |

All the configuration memory can be accessed as 8-bit bytes. When a 16-bit transfer occurs Address<0> is irrelevant. When a 32-bit transfer occurs Address<1:0> is irrelevant. Data Bus bits <7:0> are written to the address with Address<1:0>=00, bits <15:8> are written to the address with Address<1:0> = 01, etc. The Address Mode bits are

used to determine which area of the control store is to be accessed according to Table 4.

Table 4: Address Mode Selection

| Mode1    | Mode0                | Area Selected                |

|----------|----------------------|------------------------------|

| 0        | 0                    | Cell Configuration and State |

| 0        | 0 1 East/West Switch |                              |

| 1 0 Nort |                      | North/South Switch or IOB    |

| 1        | 1                    | Device Control Registers     |

## Wildcard Registers

The wildcard register allows many cell configuration memories within the same column of cells to be written simultaneously with the same data. This is used during device testing to allow regular patterns to be loaded efficiently into the control memory but is more generally useful, especially with regular bit sliced designs, since it allows many cells to be changed simultaneously. For example, a 16-bit 2:1 multiplexer could be built using cell routing multiplexers and switched between sources using a single control store access.

Similarly, the column address decoder has a wildcard register which allows several cells on the same row to be written with the same configuration. The column address decoder drives the word lines to enable particular columns of RAM cells. In this case the number of columns which can be written simultaneously is limited to 32: that is at most five don't care bits can be set.

The row and column wildcard registers can be used simultaneously to rapidly configure regular structures onto the device.

The address decoding for the XC6216 FPGA is summarized in Table 5.

Table 5: XC6216 Memory Map

| Address Bus   | Decode |                                                                  |  |  |

|---------------|--------|------------------------------------------------------------------|--|--|

|               | 00     | Cells                                                            |  |  |

| A[15:14]      | 01     | East/West Switch or IOB                                          |  |  |

| (Mode[1:0])   | 10     | North/South Switch or IOB                                        |  |  |

|               | 11     | Control Registers                                                |  |  |

|               | Cell N | Mode - Ceil column                                               |  |  |

|               | North  | /South Mode - Switch column                                      |  |  |

| A[13:8]       | Colur  | West Mode -<br>nn[5:2] = 4x4 block number<br>nn[1:0] decoded as: |  |  |

| (Column[5:0]) | 00     | West Switch                                                      |  |  |

|               | 01     | West IOB (Column[5:2]=0000)                                      |  |  |

|               | 10     | East IOB (Column[5:2]=1111)                                      |  |  |

|               | 11     | East Switch                                                      |  |  |

|               | Cell N | <i>f</i> lode                                                    |  |  |

|               | 00     | Neighbor Routing                                                 |  |  |

|               | 01     | Function Input Routing                                           |  |  |

|               | 10     | Function                                                         |  |  |

|               | 11     | State Access (Cell Registers)                                    |  |  |

| A[7:6]        | North  | /South Switch Mode                                               |  |  |

| (Column       | 00     | N/S Switch or N/S IOB Reg 0                                      |  |  |

| Offset[1:0])  | 01     | N/S Switch or N/S IOB Reg 1                                      |  |  |

| ł             | 10     | N/S Switch or N/S IOB Reg 2                                      |  |  |

|               | 11     | N/S Secondary Clock Mux<br>(Column[1:0] = 00 or 11)              |  |  |

|               | East/  | West Switch Mode                                                 |  |  |

|               | 00     | E/W Switch or E/W IOB Reg 0                                      |  |  |

|               | 01     | E/W IOB Reg 1                                                    |  |  |

|               | Cell   | Mode - Cell row                                                  |  |  |

|               |        | West Mode - Switch row                                           |  |  |

| A[5:0]        | Row[   | n/South Mode -<br>5:2] = 4x4 block number<br>1:0] decoded as:    |  |  |

| (Row[5:0])    | 00     | South Switch                                                     |  |  |

|               | 01     | South IOB (Row[5:2]=0000)                                        |  |  |

|               | 10     | North IOB (Row[5:2]=1111)                                        |  |  |

|               | 11     | North Switch                                                     |  |  |

## Serial Programming Interface

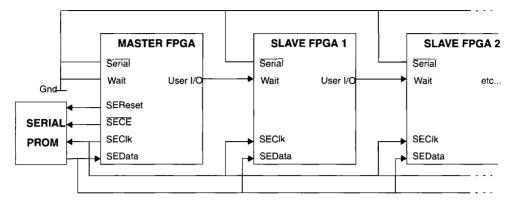

All the memory mapped locations in an XC6200 device may be written in parallel or serial mode. All the operations which can be carried out with the parallel interface may also be done serially. The serial interface gives random access to all the XC6200 memory locations. The serial interface is designed to operate with any Xilinx serial PROM. A single serial PROM may be used to configure several FPGAs. In this case one of the FPGAs acts as a 'Master' and the others as 'Slaves'. The Master controls the serial PROM and the Slaves. This is illustrated in Figure 25.

The serial PROM interface consists of 6 dedicated I/O pins:

| Serial | Input that controls transitions between states in serial mode state machine. |

|--------|------------------------------------------------------------------------------|

|        | 0 => serial mode, 1 => parallel mode                                         |

| Wait   | Input that controls transitions between states                               |

in serial mode state machine. 0 => continue loading, 1 => pause until Wait

deasserted

SEReset Output from Master FPGA that resets serial PROM address counter.

SECE Output from Master FPGA that enables serial

PROM output.

SECIK Output from Master FPGA that clocks serial PROM and slave FPGAs. SEData is clocked

into the FPGAs on the rising edge of SECIk.

SEData Serial data input to FPGA. This is sampled in the FPGA by SECIk and retimed by the

FPGA's own GClk.

In a multi-FPGA configuration a user I/O also will have to be available to provide the Wait input to the next device in the chain.

On Reset each FPGA examines its Serial and Wait inputs. Any FPGA that sees both these signals low at this time assumes it is the master and drives SEReset, SECE and SECIk. All User I/Os are held in a high-impedance state (with pull-up) until a valid configuration is loaded. In Figure 25, the User I/Os will be pulled high on Reset, hence the Wait input to the Slaves will be high and they will configure as Slaves. A valid configuration is assumed when the device ID register is loaded with the correct ID. Programmable I/Os can only be enabled when this is present.

Serial data is loaded in address/data pairs. Once an address/data pair has been shifted into the FPGA, the data word is parallel written to the corresponding address inside the FPGA just as though a parallel CPU write had occurred. This means it is possible to do all the things which can be accomplished with the parallel interface, e.g. use of the mask register, writes to cell state registers, etc.

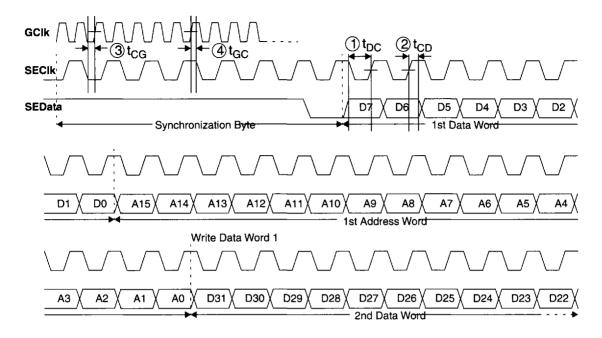

Figure 25: Master-Slave Serial Configuration

The write operation is pipelined so there need be no interruption in the serial data stream. The first address/data pair must be preceded by a Synchronization Byte = 1111\_1110. There are no start/stop bits, checksums or error check/correction bits.

The address and data are shifted in MSB first. The address is always 16-bits. The data word is initially 8-bits but may be increased to 16 or 32 bits by loading the device configuration register with the appropriate code. The bits are shifted in on the rising edge of SECIk. The SECIk rate may also be increased by writing the appropriate code to the device configuration register. Initially SECIk is 1/16 GCIk frequency. It can also be set to 1/8, 1/4 or 1/2 GCIk.

An example is shown in Figure 25. Data1 is loaded into Addr1 after the address lsb has been shifted in. In this example the first write was to the device configuration register and the data bus width was changed from 8 to 32 bits. Data word 2 starts immediately after Addr1 has been shifted in. Due to the new data bus width, 32 data bits will be shifted in. If the width had not been changed data word 2 would also have been 8 bits. Data will continue to be loaded until Serial goes high or Wait goes low.

#### **Reset And Initialization**

When the XC6200 FPGA is powered up or after a reset, all configuration memory is cleared and the cell state registers are cleared. The Reset pin is not required to be active during or after power-up to initialize the FPGA. To avoid potential high current random configurations, the power-up reset is carried out automatically. The automatic power-up initialization takes 2.5 µs. All the XC6200 I/O pads are disabled during this time and it is impossible to access the device. The XC6200 may be re-initialized at any time by asserting the Reset input for a minimum of 20 ns. This acts as a signal to the chip to initialize itself. This initialization occurs after Reset has been deasserted. Therefore there is a 1.0 µs (typ.) reset recovery time when no device accesses are possible.

# **Pin Descriptions**

The pins are labelled as follows:

#### Vpp

Connections to the nominal +5V supply. All must be connected.

#### **GND**

Connections to ground. All must be connected.

#### $\overline{CS}$

Chip Select enables the programming circuitry and initiates address decoding. When  $\overline{CS}$  is low, data can be read from or written to the control memory. This signal is intended to be used in conjunction with address decoding circuitry to select one part within a larger array for programming.

#### D<d:0>

(d+1)-bit bidirectional data bus. Used for device configuration and direct cell register access.

#### A<a:0>

Address bus for CPU access of internal registers and configuration memory. 'a' varies between family members.

#### Rd₩r

When  $\overline{CS}$  is low this signal determines whether data is read from or written to the control memory. If Rd $\overline{Wr}$  is high then a read cycle takes place. If Rd $\overline{Wr}$  is low, then a write cycle takes place.

#### GClk, GClr, G1, G2

Global signals. GClk should be used for global user clocks, GClr for global user clears and G1 and G2 for other global, low-skew signals. The GClk pin is *always* configured as an input and <u>cannot</u> be used as a fully flexible User I/O like the majority of other control signals.

#### Reset

When Reset is taken low the programming registers (mask unit and address wildcard unit) are re-initialized, resulting in the XC6200 device appearing as a conventional SRAM. The control store of the cell array is initialized into a low power consumption configuration. All programmable output pad enable signals are forced inactive. All the IO-pad pullup resistors are also enabled. This signal should be taken low immediately after power up to initialize the device. This pin is always configured as an input and cannot be used as a fully flexible User I/O like the majority of other control signals.

#### ŌĒ

When this signal is low the outputs of all programmable I/O pads are forced into a high impedance state (independent of the contents of the control store). All the IO-pad pull-up resistors are also enabled. This pin is *always* configured as an input and <u>cannot</u> be used as a fully flexible User I/O like the majority of other control signals.

#### Serial

Input which controls transitions between states in serial mode state machine.

#### Wait

Input which controls transitions between states in serial mode state machine.

0 => continue loading, 1 => pause until Wait deasserted

#### **SEReset**

Output from Master FPGA which resets serial PROM address counter.

#### SECE

Output from Master FPGA which enables serial PROM output.

#### **SECIK**

Output from Master FPGA which clocks serial PROM and slave FPGAs.

#### **SEData**

Serial data input to FPGA. This is sampled in the FPGA by SECIk and retimed by the FPGA's own GCIk.

#### ConfigOK

Signal is active (high) when a valid pattern is present in the ID register and inactive when the pattern is invalid.

#### N<sub>x</sub>

North I/Os. Connections to I/O Blocks on the north of the array.

#### Sx

South I/Os. Connections to I/O Blocks on the south of the array.

#### E,

East I/Os. Connections to I/O Blocks on the east of the array.

## $W_x$

West I/Os. Connections to I/O Blocks on the west of the array

## **Flectrical Parameters**

The XC6200 series is fabricated in 0.65 micron triple metal n-well CMOS. Foundry sources for this part have been chosen to meet or exceed relevant military standards and industry practice.

As with all CMOS devices, care must be exercised when handling this part as it can be damaged by static discharge, although standard circuit design procedures have been adopted to minimize this risk.

The power consumption of a XC6200 device can vary from a few tens to several hundreds of milliamps depending on its configuration and the data applied to it. The most significant sources of power consumption are I/O blocks and dynamic dissipation within the array, both of which are largely under user control. Dynamic power dissipation is of most concern where the XC6200 device is used to implement highly concurrent computations. Power dissipation must be considered carefully, not only because excessive dissipation could result in device failure but also because operating speed is reduced at high temperature.

A  $0.22\mu F$  decoupling capacitor across  $V_{CC}$  and GND per part is recommended. Surface mounted, radial, plastic or ceramic capacitors are suitable.

Where possible, user designs that could result in many output pads making a simultaneous transition in the same direction should be avoided. This is especially important on heavily loaded connections to non-XC6200 parts. To minimize power dissipation, redundant connections in user designs (which may arise in hierarchical design styles to promote sub-block re-use) should be deleted by CAD programs prior to programming XC6200 devices. As a general guideline, users should attempt to minimize the number of cell resources used. Where buffers must drive heavy external loads it may be helpful to choose I/O blocks near *GND* pads.

XC6200 parts automatically reset themselves after power up, since the random values in the control store at this time could correspond to a relatively high power dissipation configuration.

The XC6200 part distributes power using a redundant scheme which ensures minimal voltage drop between pads and internal circuitry. Power for pads is distributed on a separate power and ground ring.

The maximum power consumption of the XC6200 is limited by two factors: the metal conductors supplying the part and heat dissipation. The metal conductors can handle up to 100mA each. Heat dissipation is generally a much more serious consideration: a full discussion of thermal characteristics for the different package options is given in section 4 of this data book.

# **XC6200 Switching Characteristics**

Notice: The information contained in this data sheet pertains to products in the initial production phases of development. These specifications are subject to change without notice. Verify with your local Xilinx sales office that you have the latest sheet before finalizing a design.

# **XC6200 Operating Conditions**

| Symbol           | Parameter                                                                            | Min  | Max             | Units |

|------------------|--------------------------------------------------------------------------------------|------|-----------------|-------|

| ν <sub>cc</sub>  | Supply voltage relative to GND Commercial T <sub>J</sub> = 0° C to 85° C junction    | 4.75 | 5.25            | ٧     |

|                  | Supply voltage relative to GND Industrial T <sub>J</sub> = -40° C to 100° C junction | 4.50 | 5.50            | ٧     |

| V <sub>ILT</sub> | Low-level input voltage - TTL configuration                                          | 0    | 0.80            | ٧     |

| V <sub>IHT</sub> | High-level input voltage - TTL configuration                                         | 2.0  | V <sub>CC</sub> | ٧     |

| V <sub>ILC</sub> | Low-level input voltage - CMOS configuration                                         | 0    | 20%             | V     |

| V <sub>IHC</sub> | High-level input voltage - CMOS configuration                                        | 70%  | 100%            | V     |

| T <sub>IN</sub>  | Input signal transition time                                                         |      | 250             | ns    |

## XC6200 DC Characteristics Over Operating Conditions

| Symbol                       | Parameter                                | Test Conditions                                                                           | Min  | Max | Units |

|------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------|------|-----|-------|

| V <sub>OH</sub>              | High-level output voltage                | I <sub>OH</sub> = -8.0 mA<br>V <sub>DD</sub> = Min                                        | 3.86 |     | V     |

| V <sub>OL</sub>              | Low-level output voltage                 | I <sub>OL</sub> = 8mA<br>V <sub>DD</sub> = Min                                            |      | 0.4 | V     |

| I₁∟                          | Input leakage current                    | V <sub>DD</sub> = Max<br>V <sub>IN</sub> = GND or V <sub>CC</sub>                         | 10   | 10  | μА    |

| loz                          | Output high-Z leakage current            | V <sub>DD</sub> = Max<br>V <sub>O</sub> = GND or V <sub>CC</sub>                          |      | ТВА | μА    |

| CiN                          | Input capacitance for Input and I/O pins | V <sub>IN</sub> = GND<br>f = 1.0 MHz                                                      |      | 15  | pF    |

| I <sub>CC</sub> <sup>2</sup> | Quiescent Supply Current                 | $V_{IN} = V_{CC}$ or GND<br>$V_{DD} = 5 V$<br>$f = 1.0 \text{ MHz } @ 25^{\circ}\text{C}$ |      | ТВА | mA    |

Notes: 1. Sample tested.

2. Measured with no output loads, no active input pull-up resistors and all package pins at V<sub>CC</sub> or GND.

# XC6200 Absolute Maximum Ratings

| Symbol           | Parameter                                               | Value                        | Units |

|------------------|---------------------------------------------------------|------------------------------|-------|

| V <sub>CC</sub>  | Supply voltage with respect to GND                      | -0.5 to 7.0                  | ٧     |

| V <sub>IN</sub>  | DC Input voltage with respect to GND                    | -0.5 to V <sub>CC</sub> +0.5 | V     |

| V <sub>TS</sub>  | Voltage applied to 3-state output with respect to GND   | -0.5 to V <sub>CC</sub> +0.5 | V     |

| T <sub>STG</sub> | Storage temperature                                     | -65 to +150                  | Ç     |

| T <sub>SOL</sub> | Maximum soldering temperature (10s @ 1/16 in. = 1.5 mm) | +260                         | ပ္စ   |

**Warning**: Stresses beyond those listed under XC6200 Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under XC6200 Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

## XC6200 Power-on/Reset Timing Parameters

| Symbol           | Parameter                                   | Min | Тур     | Max | Units |

|------------------|---------------------------------------------|-----|---------|-----|-------|

| T <sub>WMR</sub> | Master Reset input Low pulse width          |     | 20      |     | ns    |

| T <sub>MRR</sub> | Recovery time after Master Reset deasserted |     | 1       |     | μs    |

| T <sub>PRR</sub> | Recovery time after power up                |     | 2.5     |     | μs    |

|                  | <u> </u>                                    |     | Advance |     |       |

# **XC6200 Serial Configuration Timing**

|       | Description       | Syı | mbol            | Min     | Max | Units |

|-------|-------------------|-----|-----------------|---------|-----|-------|

| SECIk | SEData setup      | 1   | T <sub>DC</sub> | TBA     | -   | ns    |

|       | SEData hold       | 2   | T <sub>CD</sub> | TBA     | -   | ns    |

|       | Setup before GClk | 3   | T <sub>CG</sub> | TBA     | -   | ns    |

|       | Hold after GClk   | 4   | T <sub>GC</sub> | TBA     | -   | ns    |

|       |                   |     |                 | Advance |     |       |

# XC6200 Global Buffer Switching Characteristic Guidelines

|                    | Speed Grade:                                                   | -   | 2    |       |

|--------------------|----------------------------------------------------------------|-----|------|-------|

| Symbol             | Parameter                                                      | Min | Max  | Units |

| T <sub>PGClk</sub> | From pad through GCIk buffer to any register clock             |     | 12   | ns    |

| T <sub>PG</sub>    | From pad through G1,G2,GCIr buffers to any register clock      |     | 12   | ns    |

| T <sub>PCIr</sub>  | From pad through global buffers to any register clear          |     | 11   | ns    |

| T <sub>PCkS</sub>  | Skew between any pair of register clocks using the same global |     | 0.9  | ns    |

| T <sub>PCIS</sub>  | Skew between any pair of register clears using the same global |     | 0.9  | ns    |

|                    | · · · · · · · · · · · · · · · · · · ·                          | Adv | ance |       |

Note: Typical loading values are used.

# XC6200 Cell Switching Characteristic Guidelines

|                     | Speed Grade                                          | :    | -2   |       |

|---------------------|------------------------------------------------------|------|------|-------|

| Symbol              | Parameter                                            | Min  | Max  | Units |

| T <sub>ILO1</sub>   | X1 change to Function Output <sup>(1)</sup>          |      | 2    | ns    |

| T <sub>ILO23</sub>  | X2/X3 change to Function Output <sup>(2)</sup>       |      | 3    | ns    |

| T <sub>ICK1</sub>   | Internal Register Set-Up Time @ X1 <sup>(1)</sup>    | 3.5  |      | ns    |

| T <sub>ICK23</sub>  | Internal Register Set-Up Time @ X2/X3 <sup>(2)</sup> | 4    |      | ns    |

| T <sub>IHCK1</sub>  | Internal Register Hold Time @ X1 <sup>(1)</sup>      | -1.5 |      | ns    |

| T <sub>IHCK23</sub> | Internal Register Hold Time @ X2/3 <sup>(2)</sup>    | -2   |      | ns    |

| T <sub>CH</sub>     | Clock High Time <sup>(3)</sup>                       | 4.5  |      | ns    |

| T <sub>CL</sub>     | Clock Low Time <sup>(3)</sup>                        | 4.5  |      | ns    |

| f <sub>TOG</sub>    | Export Control Max. flip-flop toggle rate            |      | 111  | MHz   |

| T <sub>CLW</sub>    | Clear Pulse Width <sup>(3)</sup>                     | 1    |      | ns    |

| Тско                | Clock to Function Output                             |      | 2    | ns    |

| T <sub>CKLO</sub>   | Clock to Function Output via X2/X3 feedback mux's    |      | 3    | ns    |

|                     |                                                      | Adv  | ance | Î     |

Notes: 1.Data input measured at input to X1 routing multiplexer. Clock input measured at register.

<sup>2.</sup>Data input measured at input to X2/X3 routing multiplexers. Clock input measured at register.

<sup>3.</sup>Measured at the actual register in the cell.

<sup>4.</sup> Typical loading values are used.

## XC6200 Guaranteed Input and Output Parameters (Pin-to-Pin)

All values listed below are tested directly and guaranteed over all the operating conditions. The same parameters can also be derived indirectly from the IOB and Global Buffer specifications. The delay calculator software uses this indirect method. When there is a discrepancy between these two methods, the directly tested values listed below should be used and the derived values should be ignored.

|                    | Speed Grade:                                 |          | -2  |         |      |       |

|--------------------|----------------------------------------------|----------|-----|---------|------|-------|

|                    |                                              | Best I/0 |     | I/O Wor |      | 1     |

| Symbol             | Parameter                                    | Min      | Max | Min     | Max  | Units |

| T <sub>ICKOF</sub> | Global Clock (GClk) to Output (fast)         |          |     |         | 19   | ns    |

| TICKO              | Global Clock (GClk) to Output (slew limited) |          |     |         | 22.6 | ns    |

| T <sub>PSUF</sub>  | Input Set-up Time (fast)                     |          |     | -4      |      | ns    |

| T <sub>PSU</sub>   | Input Set-up Time with delay                 |          |     | 5       | -    | ns    |

| T <sub>PHF</sub>   | Input Hold Time (fast)                       |          |     | 6.5     |      | ns    |

| T <sub>PH</sub>    | Input Hold Time with delay                   |          |     | -2.5    |      | ns    |

|                    |                                              |          | Δdv | ance    |      |       |

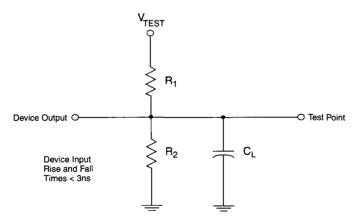

Notes: All appropriate AC specifications tested using Figure 27 as test load circuit.

These parameters are tested directly and guaranteed over the operating conditions.

As the parameters vary between I/Os, values are given for best and worst I/Os. The parameters for other I/Os will be somewhere between these two extremes. The delay calculator software will calculate the correct value for each I/O used.

All parameters assume the cell register is the closest one to the IOB.

## **XC6200 IOB Switching Characteristic Guidelines**

|                    | Speed Grade:                                        |          | -2  |           |     |       |

|--------------------|-----------------------------------------------------|----------|-----|-----------|-----|-------|

| Symbol             | Parameter                                           | Best I/O |     | Worst I/O |     | Units |

|                    |                                                     | Min      | Max | Min       | Max | 1     |

|                    | INPUT                                               | -        |     |           |     |       |

| $T_{PID}$          | Pad to Neighbor data                                |          |     |           | 4   | ns    |

| T <sub>PID4</sub>  | Pad to L4 Fastlane                                  |          |     |           | 5   | ns    |

| T <sub>PDID4</sub> | Pad to L4 Fastlane with delay                       |          |     |           | 13  | ns    |